サポートツール

現在提供中のツールリストです。 順次サポートツールを追加していきます。

EDAツールの課金金額は、会員のレベル(賛助、利用)によって開示レベルが異なりますので、CDC研事務局までお問い合わせください。 ツールによっては、ライセンス数に限りが有りますので、ライセンス取得に時間が掛かる場合がございます。 ご了承ください。 ライセンス数の追加が必要な方は、別途 ご相談ください。

一部のOpenSourceツールについてもクラウド環境にてご利用いただけます。 OpenSourceツール自身に対する課金はございませんが、クラウド環境のH/Wリソースを一部使用するため、使用するH/Wリソースに応じた費用(課金)が発生いたします

| 2022年1月1日からのサポートツール一覧 |

| ツール | 機能 | オープン | 課金形態 |

| Thunder Layout Viewer | GDSII/OASIS対応レイアウトビューアー | Now | 時間課金 |

| Thunder Basic Layout Editor | 多機能レイアウトエディタ | Now | 時間課金 |

| Thunder Advanced Layout Editor | 拡張版Thunderレイアウトエディタ | Now | 時間課金 |

| Thunder Turbo | Thunderレイアウトエディタ拡張オプション | Now | 時間課金 |

| GOLF | ジオメトリックレイアウトエディタ | Now | 時間課金 |

| GOLF PCell Designer | GOLF Pcell設計向けオプション | Now | 時間課金 |

| GOLF Schematic-Driven-Layout | GOLFスケマティックドリブンレイアウトオプション | Now | 時間課金 |

| ツール | 機能 | オープン | 課金形態 |

| Solidify | プロパティチェック、CDC プロパティベース等価検証(RTL vs Gate)等 |

オンデマンド | 優先利用 占有利用 ライセンス期間 1ヵ月間~ |

■ Cadence社製ツール一覧

時間単価ベース利用は停止中。 優先・占有利用可能は対応継続中(オンデマンドベース)。

| ツール | 機能 | オープン | 課金形態 |

| Aether-MDE-L2 | インタラクティブな設計とシミュレーション環境 | Now | 時間課金 |

| Aether-SE-L | 回路図エントリ | Now | 時間課金 |

| Aether-EMAP | EDIF入力検証 | Now | 時間課金 |

| Aether-LE-L2 | スケマティックドリブン・レイアウトエディタ | Now | 時間課金 |

| Argus-DRC-L | インタラクティブ デザインルールチェッカ | Now | 時間課金 |

| Argus-LVS-L |

レイアウトvs スケマティック検証 | Now | 時間課金 |

| スケマティック vs スケマティック検証 | Now | 時間課金 | |

| PVDB生成 | Now | 時間課金 | |

| Argus-DRC-Hierarchy | 階層レイアウト デザインルールチェッカ | Now | 時間課金 |

| Argus-LVS-Hierarchy | 階層LVS | Now | 時間課金 |

| 階層SVS | Now | 時間課金 | |

| Argus-DFM-COMMON | DFM対応DRC(45nm-65nm対応) | Now | 時間課金 |

| Argus-LVS-DFMFUN | DFM対応LVS(45nm-65nm対応) | Now | 時間課金 |

| Argus-PVE | DRC/LVSデバッガ | Now | 時間課金 |

| Argus-DRS | デザインルール入力 | Now | 時間課金 |

| デザインルールデバッガ | Now | 時間課金 | |

| ALPS | SPICE Simulator core | Now | 時間課金 |

| ALPS-Turbo | 高精度回路素子リダクション(高速化)オプション | Now | 時間課金 |

| ALPS-Pro | 高精度RCリダクションオプション | Now | 時間課金 |

| APLS-MS | IC design simulator(Verilog) | Now | 時間課金 |

| Mixed-Signal IC design simulator(Verilog-A対応) | Now | 時間課金 | |

| ALPS-CCK | Cirtuit Checker | Now | 時間課金 |

| Skipper-View | Hierarchical layout viewing tool. | Now | 時間課金 |

| Skipper-Edit | 階層的ジオメトリ編集。 IP/Cellマージ、レイアウトデータ出力 | Now | 時間課金 |

| Skipper-HTrace | ネットトレーサー | Now | 時間課金 |

| Skipper-LVL | レイアウトデータ間比較ツール | Now | 時間課金 |

| Skipper-ANA | GDSベースデザイン確認・解析ツール(P2P配線抵抗抽出など) | Now | 時間課金 |

| Skipper-ESD | EDS耐性解析ツール | Now | 時間課金 |

| Skipper-MGR | 階層移行ツール(GDSレベル階層モード、デバイスサイズの変更) | Now | 時間課金 |

| Skipper-FIB | FIB用I/Fデータ生成 | Now | 時間課金 |

| Skipper-3D | 3Dレイアウトビューワー | Now | 時間課金 |

| Skipper IPMerge | IPレイアウトデータマージ | Now | 時間課金 |

| Skipper Layoutserver | マルチスレッドマネージメント | Now | 時間課金 |

| Skipper LEFAbstractor | アンテナパラメータ付きLEF生成 | Now | 時間課金 |

| Skipper JDV | MEBES/JDVビューワ | Now | 時間課金 |

| Skipper Watermark | 電子サイン・電子透かし | Now | 時間課金 |

| ICE-TimingExplorer | MCMM対応Timing解析ツール | Now | 時間課金 |

| Qualib | IP/Library QAおよびデバッグツール | Now | 時間課金 |

| ICE-ClockExplorer | 多機能クロック構造解析(制約生成、ECO、SDCマージなど) | Now | 時間課金 |

| ICE-PowerExplorer | MMMC対応消費電力削減解析ツール | Now | 時間課金 |

| iWave | 多機能波形表示ツール | Now | 時間課金 |

| ツール | 機能 | オープン | 課金形態 |

| DesignCraft | 論理合成(Verilog-HDL/VHDL) | Now | 1日単位 |

| DesignCraft DFT Option | DFT合成オプション | Now | |

| DesignCraft Low Power Option | Low Power合成オプション | Now | |

| TimeCraft | STA(静的タイミング解析) | Now | |

| TimeCraft SI Option | SIオプション | Now | |

| TimeCraft PA Option | 電力解析オプション | Now | |

| ConstraintCraft Option | タイミング制約(SDC)チェックオプション | Now |

| ツール | 機能 | オープン | 課金形態 |

| SX-Meister | 回路設計・レイアウトシステム | Now | 占有利用 |

| Asca-Advanced | セルベース(AnaCell)のアナログ回路設計 | Now | |

| Ismo-Advanced | LSIレイアウト設計 | Now | |

| PowerVolt | 電源解析 | Now |

| ツール名 | ライセンス構成 | オープン | 課金形態 |

| Calibre Hierarchical verification with xRC | Calibre nmDRC Ap SW | NOW | 占有利用 |

| Calibre nmDRC-H Op SW | |||

| Calibre nmLVS Ap SW | |||

| Calibre nmLVS-H Op SW | |||

| Calibre RVE/QDB-H Ap SW | |||

| Calibre Interactive Ap SW | |||

| Calibre Design REV | |||

| Calibre xRC Ap SW | |||

| Calibre Hierarchical verification without xRC | Calibre nmDRC Ap SW | NOW | 占有利用 |

| Calibre nmDRC-H Op SW | |||

| Calibre nmLVS Ap SW | |||

| Calibre nmLVS-H Op SW | |||

| Calibre RVE/QDB-H Ap SW | |||

| Calibre Interactive Ap SW | |||

| Calibre Design REV | |||

| Calibre CI Op SW | |||

| Calibre ADP Op SW | |||

| Calibre Flat verification with xRC | Calibre nmDRC Ap SW | NOW | 占有利用 |

| Calibre nmLVS Ap SW | |||

| Calibre RVE/QDB-H Ap SW | |||

| Calibre Interactive Ap SW | |||

| Calibre xRC Ap SW | |||

| Calibre Flat verification without xRC | Calibre nmDRC Ap SW | NOW | 占有利用 |

| Calibre nmLVS Ap SW | |||

| Calibre RVE/QDB-H Ap SW | |||

| Calibre Interactive Ap SW | |||

| Calibre CI Op SW | |||

| Calibre ADP Op SW | |||

| Tessent Full Test with Compression | Tessent Scan(DFT Advisor) | NOW | 占有利用 |

| Tessent TestKompress AP SW | |||

| Tessent Memory BIST AP SW | |||

| Tessent MemoryBIST Repair OP SW | |||

| Tessent Boundary Scan AP SW | |||

| Tessent Logic Test with Compression | Tessent Scan(DFT Advisor) | NOW | 占有利用 |

| Tessent TestKompress AP SW | |||

| Logic Test | Tessent Fast SCAN AP SW | NOW | 占有利用 |

| Tessent Scan(DFT Advisor) | |||

| Logic BIST | Tessent Logic BIST AP SW | NOW | 占有利用 |

| Memory BIST | Tessent Memory BIST AP SW | NOW | 占有利用 |

| Questa CDC-FX Op SW | NOW | 占有利用 | |

| Questa Verification IP Library Ap SW | NOW | 占有利用 | |

| Questa CDC Ap SW | NOW | 占有利用 | |

| Questa Ultra Bnd SW | NOW | 占有利用 | |

| Questa Core LNL Ap SW | NOW | 占有利用 | |

| Questa Core MixedHDL Ap SW | NOW | 占有利用 | |

| Questa Prime Ap SW | NOW | 占有利用 | |

| Questa ADMS Core MixedHDL Bnd SW | NOW | 占有利用 | |

| Questa Formal AutoCheck Ap SW | NOW | 占有利用 | |

| Questa Formal CoverCheck Op SW | NOW | 占有利用 | |

| Questa Formal PropCheck Op SW | NOW | 占有利用 | |

| ツール | 機能 | オープン | 課金形態 |

| ASCENT Lint | 早期RTL機能検証(RTL Lintチェッカ) STARCルール対応 |

Now | 優先利用 占有利用 ライセンス期間 2ヵ月間~ |

| MERIDIAN RXV | RTLレベル静的不定(X)伝搬検証ツール ブロック初期化、リセット最適化 |

Now |

| ツール | 機能 | オープン | 課金形態 |

| TurboBSD | バウンダリSacn対応ツール | Now | プロジェクトベース |

| TurboScan | フルScan用ツール | Now | |

| VirtualScan | チップ内アクセス用Scan回路インプリツール | Now | |

| TurboBIST-Memory | メモリBIST(SRAM, ROM, DRAM, CAM対応) | Now |

※サポートツールの追加については、各EDAベンダーと協議中です

提供ハードウエア

CDC研究所のハードウエア費用には、アクセスプロキシー(ログイン認証)、ユーザ管理、NFSサーバー、仮想マシーン(VM)間ネットワーク、クラウド内データ通信料金の全てを含みます。

仮想マシーン(VM)料金は、ユーザーID毎に1日(24Hr)当たりの金額です。 1日当たり、同じサイズの仮想マシーン(VM)を何度使用しても積算時間が24Hr以内であれば一定の料金となります

異なるVMを使用した場合には、それぞれのVM使用に対し1日分の料金を適用いたします

| 仮想マシーンタイプ(VM) | vCPU数、メモリ容量 | 課金(1日当たり) |

| L5.micro | vCPU x 1, Memory 4GB | 1,000円 |

| L5.small | vCPU x 2, Memory 8GB | 2,000円 |

| L5.medium | vCPU x 8, Memory 12GB | 3,000円 |

| L5.large | vCPU x 16, Memory 24GB | 8,000円 |

| L5.Xlarge | vCPU x 16, Memory 32GB | 10,000円 |

ディスクサーバー利用料金(1プロジェクト、500GB当たり)

| ディスク容量 | 課金額 |

| 500GB/プロジェクト | 350円/日 |

| バックアップ/500GB | 350円/日 |

各EDA利用会員には、プロジェクト毎に500GBのディスク領域をデフォルト設定いたします

アサインされたディスク領域は、プロジェクトにアサインされたユーザが自由に使用することが可能です

同一プロジェクトに割当てられた設計者は、異なるVM(Virtual Machine)から同じディスクを参照する事ができ、設計データの共有が可能です。 異なるプロジェクトに割り当てた場合には、クラウド環境上ではパス、マウント等が許可されませんので、ディスク領域を共有することはできません

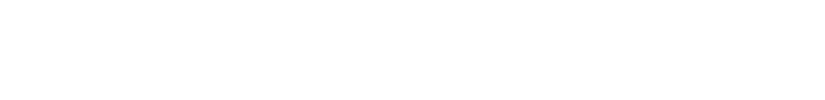

ライセンスイメージ(一般)

実際にEDAツールをご利用いただく場合の手順です。 一般と特定EDAベンダー向けとがあります。 各様式は、ドキュメントのサイトから入手可能です

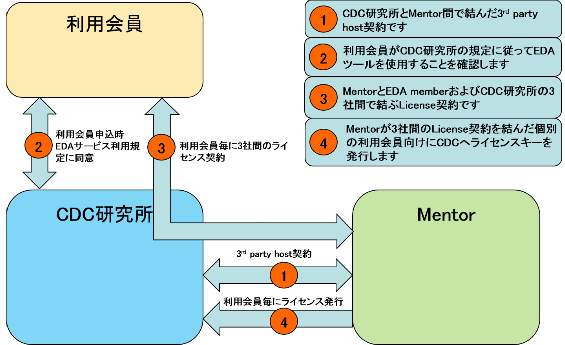

ライセンスイメージ(Mentor)

実際にEDAツールとしてMentor社ツールをご利用いただく場合の手順です。 各様式は、ドキュメントのサイトから入手可能です